目录

4.双向data-lane,可以选择只支持双向HS或Escape

9.DPHY可以直接传输8bit原始数据也可以用8b/9b编码

10.HS的反向速率只有正向速率的1/4,反向的接收端需要调整选择合适的clk相位

11.DPHY 三个operating Mode :control、HS、Escape

12.DPHY最小传输单元是Byte,数据量是byte整数倍

1.DPHY的输出差分clk是双沿有效

所以DDRCLKHs_I/Q 频率是ByteCLKHS的4倍。ByteclkHs频率是bitrate的1/8.但是这些频率和pixclk的关系是不确定的,因为burst传输下,保证所有差分线上bitrate之和大于pixclk domian的bitrate就行。

2.LP和Escape这些低功耗传输是单端的

差分是两根线上电压在均值上下对称摆动,任意时刻两根线上电压都是相对均值电压对称的,设均值电压为V,则两根线上电压是V+Vswing/2和V-Vswing/2.

单端就是线上电压只和地线做参考,线与线之间的电压没有关系。LP和Escape 低功耗模式下,Dp和Dn各自以0和1.2V电压传输数据。

LP state但也不是Escape mode的情况下【即Control Mode】,主要是传输一些LP的状态或序列来控制PHY是在stop状态还是进入其他状态。比如说data-lane通过LP-11,LP-10,LP-00,LP-01,LP-00序列进入Escape mode。这种情况下clk lane是没有是时钟的。每一个LP 状态都会有一定的持续时间,所有rx端在一定时间内检测到LP电平变化就行,不需要clk【clk lane处于Esc的LP-00 space状态还是Control Mode的stop state LP-11?】。

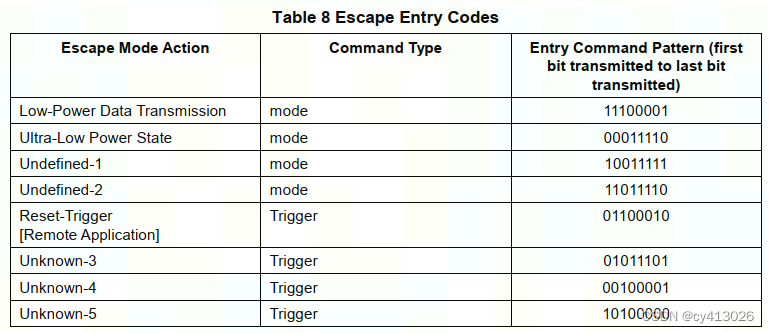

Escape mode 所有传输都是用spaced-ont-hot(间隔独热码)编码,是不需要时钟的异步传输,只是需要用Dp ^ Dn来获得EscClk时钟。

3.Contention Detection (竞争检测)

如果两个PHY都是双向时,为了防止两端的PHY同时驱动总线而发生冲突,协议要求PHY必须支持contention detection模块,简称CD模块

4.双向data-lane,可以选择只支持双向HS或Escape

很多情况下,为了成本考虑,没必要支持反向的HS传输,也没有太多这样的场景。此时就只支持反向的Esc

5.传输数据和命令只能在HS和Esc的LPDT

6.正向Esc必须支持ULPS和Triggers

7.ULPS是什么样的状态

首先ULPS是控制TX/RX的PHY及protocol的clk和power状态吗?此时差分线是不是可以下电?

ULPS状态且ulpsActiveNot=0时,TX protocl layer可以关闭TxClkEsc【注意和clkLane状态不是一回事】。对应Rx那边也不能从dataLane异或出RxClkEsc,且要上报protocol,当前是ULPS。dataLane处在LP-00状态。

至于下电 目前并没有看到 这么做。是ULPS的范围太小了,而且还要快速被Wakeup,所以没有用来控制下电?

8.clk lane只支持Escape的ULPS

由于clk lane不传输数据和命令,所以要么在HS下传时钟,要么在Esc的ULPS状态下LP-00或者contorl mode下stop 状态LP-11。clk lane的进入Escape程序不像dataLane需要LP-11,LP-10,LP-00,LP-01,LP-00,而是直接LP-11,LP-10,LP-00。

只有HS传输才需要clk,所以当所有的dataLane都不在HS传输后,可以关闭clklane

9.DPHY可以直接传输8bit原始数据也可以用8b/9b编码

10.HS的反向速率只有正向速率的1/4,反向的接收端需要调整选择合适的clk相位

因为反向传输,只是datalane的方向发生了变化,clklane没变,所以反向后的Tx【slave侧】用的是反向后的Rx【master】那边输出的ddr clk。数据经过line delay和在master,slave的内部delay。达到master侧采样点时,有一个固定的未知的delay。所以在master接收侧需要首先利用slave在SOT发送的sync sequence进行synchronization。

11.DPHY 三个operating Mode :control、HS、Escape

如果dataLine不在HS和Escape mode,那就一定在control mode。control mode的stop state LP-11可以作为clk lane/data lane的待机state。

12.DPHY最小传输单元是Byte,数据量是byte整数倍

DPHY没有规定最大的burst传输长度,但是PHY没有有效的错误恢复处理,实际误码率不会是0,所以需要合理的选择最大burst Length;而对于短burst,header和trailer的时间可能比payload还长。

13.多dataLane传输时,它们可以独立的开始和结束

多个dataLane可以传输不同数据量,也可以在不同时间开始和结束。但一般情况下所有dataLane都是同时开始的,结束时间不一样。

14.Remote Triggers

是TX protocol层通过Escape mode发送到对端protocol layer的一个flag,不会影响PHY的行为。Reset-Trigger就是协议已经定义的Triggers。目前还没看到除此之外的其他协议定义的Triggers。

15.DPHY的初始化

上电之后,master PHY会被系统或PPI接口初始化,此时需要master PHY驱动LP-11 stop state超过Tinit时间。需要注意的是第一个持续超过Tinit的stop state 才是初始化period。

slave PHY是检测到第一个超过Tinit的stop state时,才被初始化。在没有检测到第一个超过Tinit的stop state之前,所有的line state。

多lane配置,要同时初始化。

16.Calibration

- 只有超过1.5Gbps的 transmitter在初始化时必须通过Calibration deskew。

- 周期性deskew是可选的

- 小于等于1.5Gbps的传输,deskew是可选的

- 当从其他状态转到HS rate > 1.5Gbps, deskew也是可选的

- deskew调整的是clklane与datalane之间的skew

TX先发16'hFFFF作为sync pattern;

接着在发至少2^15个0101用来initial deskew calibration

周期性校准只需要发至少2^10 个0101

校准之后再发送HS的同步序列:‘00011101’ 【0x1D】

17.clklane扩频

dphy clklane可以进行频率扩频调制用以降低EMI。clk lane的ddr变化沿在发送端是和数据中间对齐的,而不是和数据变化对齐

18.Escape进入流程

LP11->LP10->LP00-LP01->LP00

其内的LPDT/ULPS/Triggers子状态还有专门的entry command

19.SOT/EOT/BTA

SOT: start of transmission

HS的同步序列就是在SOT阶段发送的。

EOT: end of transmission

BTA: Bus turn-around

以上每一个过程都有专用处理流程,可以参见

| Specification for D-PHY Version 1.2.pdf |